Prodigy推出PGY-PCIeLP-SBA邊帶信號分析儀

芯片供應商需要驗證 DUT 不同狀態下邊帶信號的電氣時序測量,并查看長期一致性。

為了滿足這一要求,Prodigy

Technovations 開發了 c它監控這些信號并提供多周期運行中測量的統計信息,以確保穩定可靠的運行。PGY-PCIeLP-SBA

包括 discovery 系列邏輯分析儀(掌上大小),帶有用于 REFCLK 的 PCIe 邊帶信號分析的定制邏輯、用于查看結果和調試功能的軟件、帶有 M.2 擴展板的飛線探針,可訪問邊帶信號。

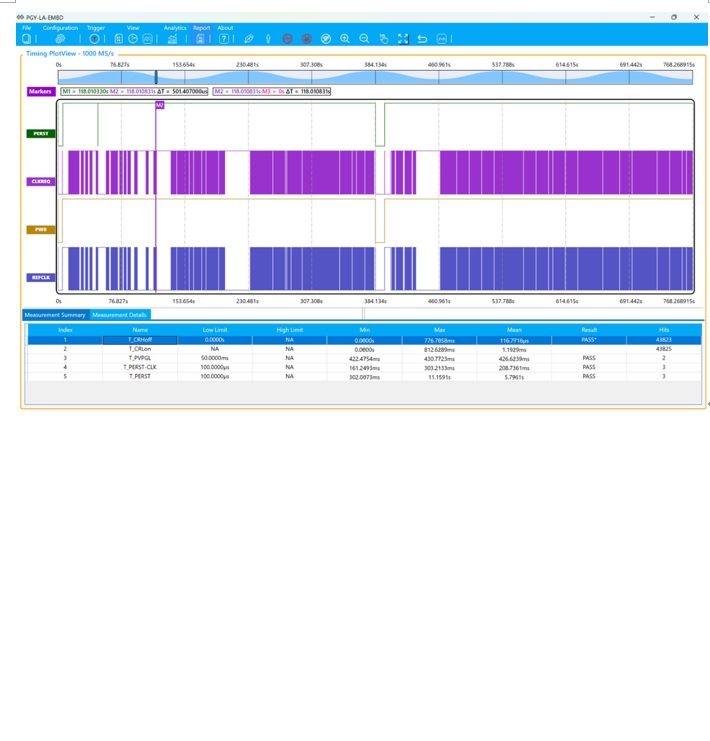

PGY-PCIeLP-SBA 在不同工作條件下監控 M.2 接口的 CLKREQ、REFCLK、PERSET 和 PWR 信號。它根據 PCIe 和 M.2 接口規范文檔提供這些信號的時序測量。用戶還可以在特定的時序測量失敗時設置基于硬件的觸發器并獲得通知。API 支持用戶對 DUT 進行長時間測試。用戶界面顯示時序圖,并帶有 100MHz

REFCLK 條件、低功耗狀態、重啟和電源回收以及運行測試用例期間的電源打開狀態的抽象視圖。

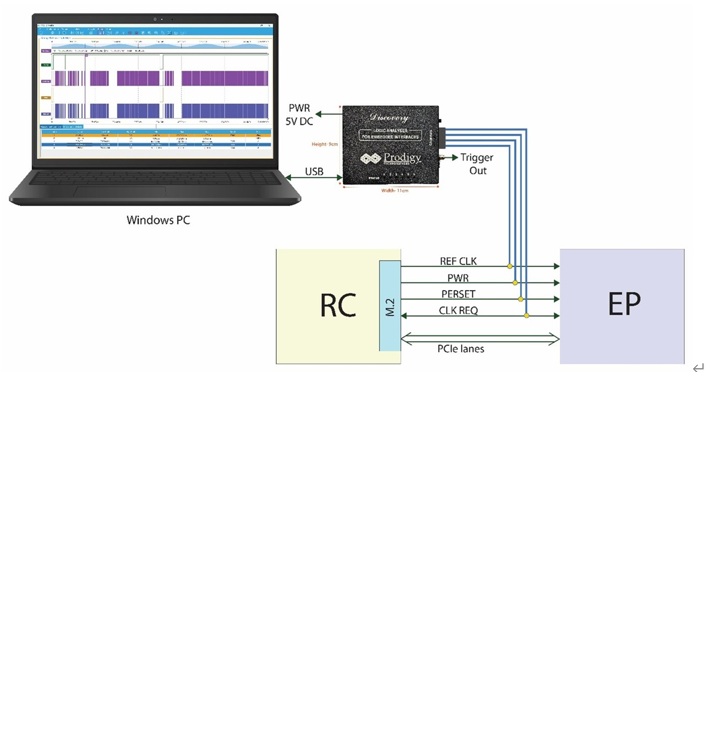

PCIe 邊帶信號分析的典型測試設置為:

PGY-PCIeLP-SBA 具有 M.2 擴展板,可訪問所有側帶信號,這些信號可以連接到 PCIe 低功耗側帶信號分析儀。該軟件在 Windows PC 中運行,可以配置 Analyzer 進行測量和觸發條件。它持續繪制時序波形并更新時序測量摘要、統計數據和詳細信息

軟件會自動檢測開機測試、低功耗進出測試、重啟測試和突然斷電測試。它將對所有這些測試用例進行適用的測量,并以列表形式報告結果。它還將提供 timing

measurements 的統計信息和 side band 信號的 timing

diagram 的連續圖。

用戶可以將測量詳細信息列表視圖中的任何特定 timing 測量值與 timing

waveform 圖相關聯,以定位此事件。

用戶可以在列表視圖中對通過或失敗的結果進行排序。如果任何特定的 timing

measurement 需要與具有所有測試用例的完整數據的 timing

waveform 相關,則用戶單擊 timing measurements 可在 timing

waveform 中找到它。

為了有效地捕獲難以捉摸的事件,PGY-PCIeLP-SBA 在時序測量失敗時提供觸發器。pre 和 post trigger

數據使用戶能夠查看 trigger event 和 post trigger

event 之前的數據,以確定 timing failure 的可能原因。trigger 并將 timing

measurement 與 timing diagrams 相關聯使其成為一種高效的 debugging 工具。

PGY-PCIeLP-SBA PCIe邊帶信號分析儀是業界首臺帶有軟件的便攜式儀器,可以在 PCIe 接口的不同狀態下分析儀帶信號。PGY-PCIeLP-SBA

中包含的 Discovery 邏輯分析儀還支持 I3C 和 I2C(SM 總線)接口的觸發和協議解碼。這使得它成為完整、低成本、易于使用的儀器,適用于任何設計、硅前和硅后測試和現場工程師,以驗證和調試邊帶信號。

想要了解更多信息?加入我們的網絡研討會,主題為“開機和低功耗狀態下的PCIe邊帶信號功能概述,以及驗證。

Prodigy

Technovations 提供 PCIe 低功耗邊帶信號分析儀,幫助您捕獲和分析電源轉換期間的關鍵信號行為。