上海電感電子元器件鍍金貴金屬

鍍金層對元器件的可焊性有影響,理論上金具有良好的可焊性,但實際情況中受多種因素影響,可能會導(dǎo)致可焊性變差1。具體如下1:從理論角度看:金的化學(xué)性質(zhì)穩(wěn)定,不易氧化,能為焊接提供良好的表面條件。鍍金層可以使電子元器件表面更容易與焊料結(jié)合,降低焊接過程中金屬表面氧化層的影響,有助于提高焊接質(zhì)量和可靠性,減少虛焊、脫焊等問題的發(fā)生。從實際情況看:孔隙率問題:金鍍層的孔隙率較高,當(dāng)金鍍層較薄時,容易在金鍍層與其基體(如鎳或銅)之間因電位差產(chǎn)生電化學(xué)腐蝕,從而在金鍍層表面形成一種肉眼不可見的氧化物層。這層氧化物會阻礙焊料與鍍金層的潤濕和結(jié)合,導(dǎo)致可焊性下降。有機污染問題:鍍金層易于吸附有機物質(zhì),包括鍍金液中的有機添加劑等,容易在其表面形成有機污染層。這些有機污染物會使焊料不能充分潤濕基體金屬或鍍層金屬,進而影響焊接質(zhì)量,造成虛焊等問題。鍍金電子元器件在高溫高濕環(huán)境下,仍保持良好性能。上海電感電子元器件鍍金貴金屬

鍍金層的孔隙率過高會對電子元件產(chǎn)生諸多危害,具體如下:加速電化學(xué)腐蝕:孔隙會使底層金屬如鎳層暴露在空氣中,在潮濕或高溫環(huán)境中,暴露的鎳層容易與空氣中的氧氣或助焊劑中的化學(xué)物質(zhì)發(fā)生反應(yīng),形成氧化鎳或其他腐蝕產(chǎn)物,進而加速電子元件的腐蝕,縮短其使用壽命。降低焊接可靠性:孔隙會導(dǎo)致焊接點的金屬間化合物不均勻分布,影響焊接強度和導(dǎo)電性能,使焊接點容易出現(xiàn)虛焊、脫焊等問題,降低電子元件焊接的可靠性,嚴(yán)重時會導(dǎo)致電路斷路,影響電子設(shè)備的正常運行。增大接觸電阻:孔隙的存在可能使鍍金層表面不夠致密,影響電子元件的導(dǎo)電性,導(dǎo)致接觸電阻增大。這會增加信號傳輸過程中的能量損失,影響信號的穩(wěn)定性和清晰度,對于高頻信號傳輸?shù)碾娮釉赡軙斐尚盘査p和失真。引發(fā)接觸故障:若基底金屬是銅,銅易向鍍金層擴散,當(dāng)銅擴散到表面后會在空氣中氧化生成氧化銅膜。同時,孔隙會使鎳暴露在環(huán)境中,與大氣中的二氧化硫反應(yīng)生成硫酸鎳,該生成物絕緣且體積較大,會沿微孔蔓延至鍍金層上,導(dǎo)致接觸故障,影響電子元件的正常工作。貴州航天電子元器件鍍金貴金屬鍍金結(jié)合力強,耐磨耐用,同遠(yuǎn)技術(shù)讓元器件更可靠。

鎳層不足導(dǎo)致焊接不良的原因形成黑盤1:鎳原子小于金原子,鍍金后晶粒粗糙,鍍金液可能會滲透到鎳層并將其腐蝕,形成黑色氧化鎳,其可焊性差,使用錫膏焊接時難以形成冶金連接,導(dǎo)致焊點易脫落。金屬間化合物過度生長1:鎳層厚度小,焊接時形成的金屬間化合物(IMC)總厚度會越大,且 IMC 會大量擴展到界面底部。IMC 的富即會導(dǎo)致焊點脆性增加,在老化后容易出現(xiàn)脆性斷裂,降低焊接強度。無法有效阻隔銅7:鎳層能夠阻止銅溶蝕入焊點的錫中而形成對焊點不利的合金。鎳層不足時,這種阻隔作用減弱,銅易與錫形成不良合金,影響焊點壽命和焊接可靠性。鍍層孔隙率增加:如果鎳層沉積過程中厚度不足,可能會存在孔隙、磷含量不均勻等問題,焊接時容易形成不均勻的脆性相,加劇界面脆化,導(dǎo)致焊接不良。

選擇適合特定應(yīng)用場景的鍍金層厚度,需要綜合考慮電氣性能要求、使用環(huán)境、插拔頻率、成本預(yù)算及工藝可行性等因素,以下是具體分析:電氣性能要求2:對于高頻電路或?qū)π盘杺鬏斠蟾叩膱鼍埃绺咚贁?shù)字電路,為減少信號衰減和延遲,需較低的接觸電阻,應(yīng)選擇較厚的鍍金層,一般2μm以上。對于電流承載能力要求高的情況,如電源連接器,也需較厚鍍層來降低電阻,可選擇5μm及以上的厚度。使用環(huán)境3:在高溫、高濕、高腐蝕等惡劣環(huán)境下,如航空航天、海洋電子設(shè)備等,為保證元器件長期穩(wěn)定工作,需厚鍍金層提供良好防護,通常超過3μm。而在一般室內(nèi)環(huán)境,對鍍金層耐腐蝕性要求相對較低,普通電子接插件等可采用0.1-0.5μm的鍍金層。插拔頻率7:對于頻繁插拔的連接器,成本預(yù)算1:鍍金層越厚,成本越高。對于大規(guī)模生產(chǎn)的消費類電子產(chǎn)品,在滿足基本性能要求下,為控制成本,會選擇較薄的鍍金層,如0.1-0.5μm。對于高層次、高附加值產(chǎn)品,工藝可行性:不同的鍍金工藝有其適用的厚度范圍,過厚可能導(dǎo)致鍍層不均勻、附著力下降等問題。例如化學(xué)鍍鎳-金工藝,鍍金層厚度通常有一定限制,需根據(jù)具體工藝能力來選擇合適的厚度,確保能穩(wěn)定實現(xiàn)所需鍍層質(zhì)量。電子元器件鍍金,賦予優(yōu)異抗變色性,保持外觀與功能。

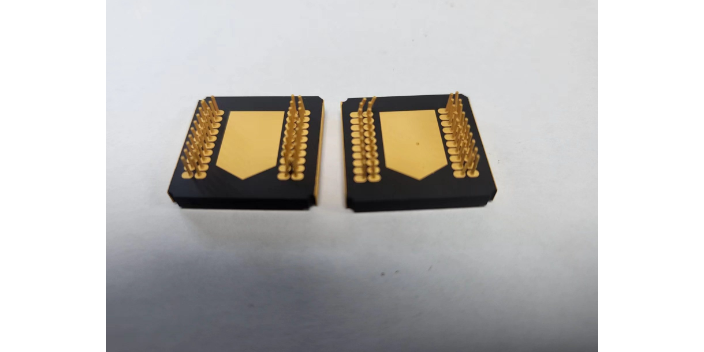

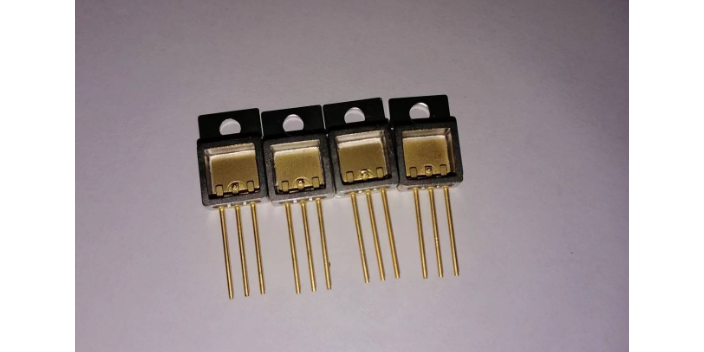

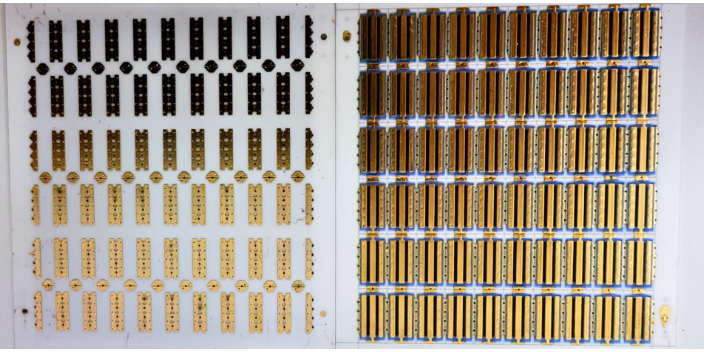

在電子元件制造領(lǐng)域,鍍金這一表面處理技術(shù)發(fā)揮著不可替代的作用。首先,它能***提升電子元件的導(dǎo)電性能。金作為一種優(yōu)良導(dǎo)體,當(dāng)鍍在元件表面,可有效降低電阻值。像在高頻電路里,電阻的微小降低就能減少信號傳輸過程中的損失,保障信號高效、穩(wěn)定傳遞。其次,金具有高度的化學(xué)穩(wěn)定性,鍍金層宛如堅固的“鎧甲”,可防止電子元件被氧化、腐蝕。電子設(shè)備常處于復(fù)雜環(huán)境,潮濕空氣、腐蝕性氣體等都會侵蝕元件,鍍金后能大幅延長元件使用壽命,確保其在惡劣條件下穩(wěn)定工作。再者,鍍金能改善電子元件的可焊性。焊接時,金的良好潤濕性讓焊料與元件緊密結(jié)合,避免虛焊、短路等焊接問題,提升產(chǎn)品質(zhì)量與可靠性。同時,鍍金還為元件帶來美觀的金黃色外觀,增添產(chǎn)品***感,在一些**電子產(chǎn)品中,鍍金元件兼具裝飾與實用功能。電子元器件鍍金,提升導(dǎo)電性,讓信號傳輸更穩(wěn)定高效。四川高可靠電子元器件鍍金廠家

電子元器件鍍金,通過均勻鍍層,優(yōu)化散熱與導(dǎo)電效率。上海電感電子元器件鍍金貴金屬

檢測鍍金層結(jié)合力的方法有多種,以下是一些常見的檢測方法:彎曲試驗操作方法:將鍍金的電子元器件或樣品固定在彎曲試驗機上,以一定的速度和角度進行彎曲。通常彎曲角度在 90° 到 180° 之間,根據(jù)具體產(chǎn)品的要求而定。對于一些小型電子元器件,可能需要使用專門的微型彎曲夾具來進行操作。結(jié)果判斷:觀察鍍金層在彎曲過程中及彎曲后是否出現(xiàn)起皮、剝落、裂紋等現(xiàn)象。如果鍍金層能夠承受規(guī)定的彎曲次數(shù)和角度而不出現(xiàn)明顯的結(jié)合力破壞跡象,則認(rèn)為結(jié)合力良好;反之,如果出現(xiàn)上述缺陷,則說明結(jié)合力不足。劃格試驗操作方法:使用劃格器在鍍金層表面劃出一定尺寸和形狀的網(wǎng)格,網(wǎng)格的大小和間距通常根據(jù)鍍金層的厚度和產(chǎn)品要求來確定。一般來說,對于較薄的鍍金層,網(wǎng)格尺寸可以小一些,如 1mm×1mm;對于較厚的鍍金層,網(wǎng)格尺寸可適當(dāng)增大至 2mm×2mm 或 5mm×5mm。然后用膠帶粘貼在劃格區(qū)域,膠帶應(yīng)具有一定的粘性,能較好地粘附在鍍金層表面。粘貼后,迅速而均勻地將膠帶撕下。結(jié)果判斷:根據(jù)劃格區(qū)域內(nèi)鍍金層的脫落情況來評估結(jié)合力。按照相關(guān)標(biāo)準(zhǔn),如 ISO 2409 或 ASTM D3359 等標(biāo)準(zhǔn)進行評級。上海電感電子元器件鍍金貴金屬

- 上海電感電子元器件鍍金貴金屬 2025-07-09

- 河北陶瓷金屬化電子元器件鍍金車間 2025-07-09

- 湖北片式電子元器件鍍金鎳 2025-07-08

- 陜西共晶電子元器件鍍金生產(chǎn)線 2025-07-08

- 陜西光學(xué)電子元器件鍍金供應(yīng)商 2025-07-08

- 廣東氧化鋁電子元器件鍍金加工 2025-07-08

- 高可靠電子元器件鍍金廠家 2025-07-08

- 陜西五金電子元器件鍍金生產(chǎn)線 2025-07-08

- 福建片式電子元器件鍍金貴金屬 2025-07-07

- 浙江薄膜電子元器件鍍金專業(yè)廠家 2025-07-07

- 電鍍電源igbt模塊IGBT IPM智能型功率模塊 2025-07-09

- 上海電感電子元器件鍍金貴金屬 2025-07-09

- 標(biāo)準(zhǔn)AH402F貨源充足 2025-07-09

- OS02G10攝像頭模組 2025-07-09

- 長寧區(qū)質(zhì)量機械電氣設(shè)備報價 2025-07-09

- 紹興瞬變抑制二極管分類 2025-07-09

- 嘉興電木ksd301溫控器 2025-07-09

- 貿(mào)易AH402F是什么 2025-07-09

- 南昌工業(yè)級無線數(shù)傳模塊 2025-07-09

- 進口半導(dǎo)體器件設(shè)計 2025-07-09