湖北了解PCB制板包括哪些

4.4 成本控制在 PCB 制版過程中,成本控制是企業關注的重點之一。成本主要包括材料成本、制版成本、加工成本等多個方面。在材料選擇上,要在滿足性能要求的前提下,選擇性價比高的材料。例如,對于一些對性能要求不是特別高的消費類電子產品,可以選用普通的 FR - 4 覆銅板,而避免使用價格昂貴的**材料。在設計階段,通過優化設計,減少元器件數量、簡化電路結構、合理選擇封裝形式等方式,可以降低材料成本和加工成本。例如,盡量選用通用的元器件,避免使用特殊規格或定制的元器件,以降低采購成本;采用合適的封裝形式,如表面貼裝封裝(SMT)相比傳統的通孔插裝封裝(THT),可以提高生產效率,降低焊接成本。此外,合理控制制版工藝要求,如選擇合適的線寬、線距、層數等,避免過高的工藝要求導致制版成本大幅增加。同時,與制版廠進行充分溝通,了解其報價結構和優惠政策,通過批量生產、長期合作等方式爭取更優惠的價格。在現代電子技術的發展中,印刷電路板(PCB)制版無疑是一個至關重要的環節。湖北了解PCB制板包括哪些

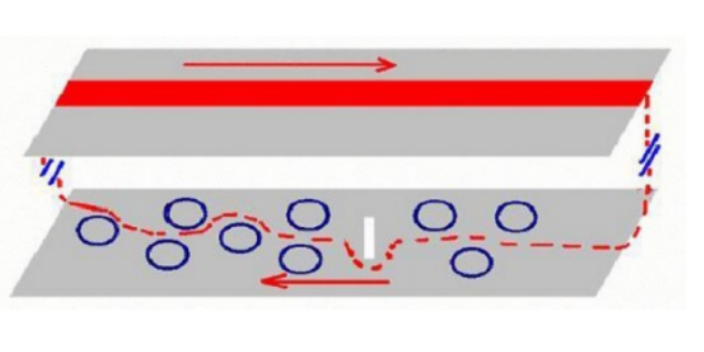

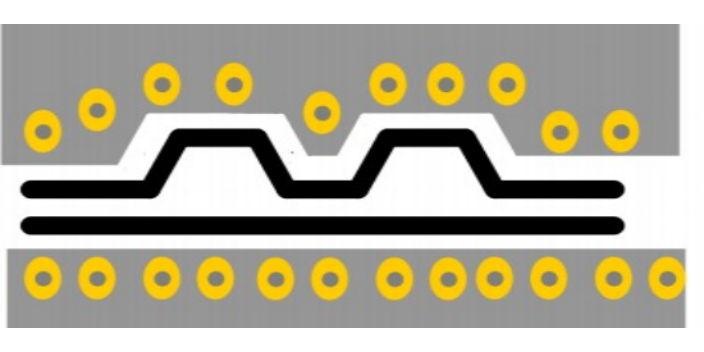

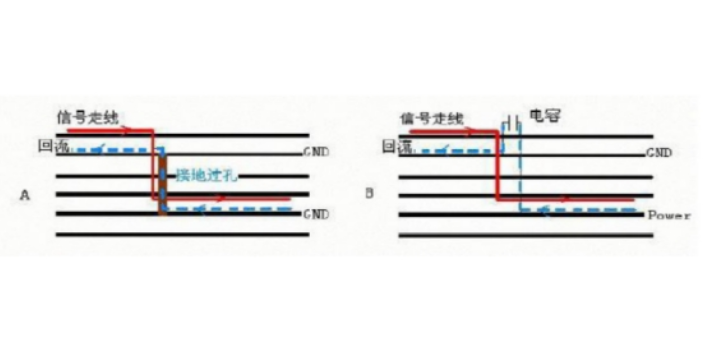

PCB疊層設計在設計多層PCB電路板之前,設計者需要首先根據電路的規模、電路板的尺寸和電磁兼容(EMC)的要求來確定所采用的電路板結構,也就是決定采用4層,6層,還是更多層數的電路板。確定層數之后,再確定內電層的放置位置以及如何在這些層上分布不同的信號。這就是多層PCB層疊結構的選擇問題。層疊結構是影響PCB板EMC性能的一個重要因素,也是抑制電磁干擾的一個重要手段。本節將介紹多層PCB板層疊結構的相關內容。對于電源、地的層數以及信號層數確定后,它們之間的相對排布位置是每一個PCB工程師都不能回避的話題;層的排布一般原則:1、確定多層PCB板的層疊結構需要考慮較多的因素。從布線方面來說,層數越多越利于布線,但是制板成本和難度也會隨之增加。對于生產廠家來說,層疊結構對稱與否是PCB板制造時需要關注的焦點,所以層數的選擇需要考慮各方面的需求,以達到佳的平衡。對于有經驗的設計人員來說,在完成元器件的預布局后,會對PCB的布線瓶頸處進行重點分析。結合其他EDA工具分析電路板的布線密度;再綜合有特殊布線要求的信號線如差分線、敏感信號線等的數量和種類來確定信號層的層數;然后根據電源的種類、隔離和抗干擾的要求來確定內電層的數目。這樣。黃岡定制PCB制板報價全流程追溯系統:從材料到成品,掃碼查看生產履歷。

配置板材的相應參數如下圖2所示,本例中為缺省值。圖2配置板材的相應參數選擇Design/Rules選項,在SignalIntegrity一欄設置相應的參數,如下圖3所示。首先設置SignalStimulus(信號激勵),右鍵點擊SignalStimulus,選擇Newrule,在新出現的SignalStimulus界面下設置相應的參數,本例為缺省值。圖3設置信號激勵*接下來設置電源和地網絡,右鍵點擊SupplyNet,選擇NewRule,在新出現的Supplynets界面下,將GND網絡的Voltage設置為0如圖4所示,按相同方法再添加Rule,將VCC網絡的Voltage設置為5。其余的參數按實際需要進行設置。點擊OK推出。圖4設置電源和地網絡*選擇Tools\SignalIntegrity…,在彈出的窗口中(圖5)選擇ModelAssignments…,就會進入模型配置的界面(圖6)。圖5圖6在圖6所示的模型配置界面下,能夠看到每個器件所對應的信號完整性模型,并且每個器件都有相應的狀態與之對應,關于這些狀態的解釋見圖7:圖7修改器件模型的步驟如下:*雙擊需要修改模型的器件(U1)的Status部分,彈出相應的窗口如圖8在Type選項中選擇器件的類型在Technology選項中選擇相應的驅動類型也可以從外部導入與器件相關聯的IBIS模型,點擊ImportIBIS。

PCB制板,即印刷電路板制造,作為現代電子設備的重要組成部分,其工藝和技術的進步對于電子產業的發展起著至關重要的推動作用。在這個信息技術飛速發展的時代,PCB制板不僅是連接電子元件的橋梁,更是承載著復雜電路功能的重要平臺。精湛的PCB設計和制造工藝,使得各類電子產品如智能手機、計算機、家用電器等得以高效運作,使我們的生活變得更加便捷和智能。在PCB制板的過程中,設計是第一步,設計師需要準確理解電路的功能需求,從而繪制出邏輯清晰、排布合理的電路圖。

PCB制版是一個復雜而精密的工藝過程。

Inner_1),GND(Inner_2),Siganl_2(Bottom)。(3)POWER(Top),Siganl_1(Inner_1),GND(Inner_2),Siganl_2(Bottom)。顯然,方案3電源層和地層缺乏有效的耦合,不應該被采用。那么方案1和方案2應該如何進行選擇呢?一般情況下,設計人員都會選擇方案1作為4層板的結構。選擇的原因并非方案2不可被采用,而是一般的PCB板都只在頂層放置元器件,所以采用方案1較為妥當。但是當在頂層和底層都需要放置元器件,而且內部電源層和地層之間的介質厚度較大,耦合不佳時,就需要考慮哪一層布置的信號線較少。對于方案1而言,底層的信號線較少,可以采用大面積的銅膜來與POWER層耦合;反之,如果元器件主要布置在底層,則應該選用方案2來制板。如果采用如圖11-1所示的層疊結構,那么電源層和地線層本身就已經耦合,考慮對稱性的要求,一般采用方案1。6層板在完成4層板的層疊結構分析后,下面通過一個6層板組合方式的例子來說明6層板層疊結構的排列組合方式和方法。(1)Siganl_1(Top),GND(Inner_1),Siganl_2(Inner_2),Siganl_3(Inner_3),POWER(Inner_4),Siganl_4(Bottom)。方案1采用了4層信號層和2層內部電源/接地層,具有較多的信號層。批量一致性:全自動生產線,萬片訂單品質誤差<0.02mm。荊門設計PCB制板布線

隨著智能科技的發展,對PCB制板的要求也越來越高。湖北了解PCB制板包括哪些

在高速數字系統中,由于脈沖上升/下降時間通常在10到幾百p秒,當受到諸如內連、傳輸時延和電源噪聲等因素的影響,從而造成脈沖信號失真的現象;在自然界中,存在著各種各樣頻率的微波和電磁干擾源,可能由于很小的差異導致高速系統設計的失敗;在電子產品向高密和高速電路設計方向發展,解決一系列信號完整性的問題,成為當前每一個電子設計者所必須面對的問題。業界通常會采用在PCB制板前期,通過信號完整性分析工具盡可能將設計風險降,從而也促進了EDA設計工具的發展……信號完整性(SignalIntegrity,簡稱SI)問題是指高速數字電路中,脈沖形狀畸變而引發的信號失真問題,通常由傳輸線阻抗不匹配產生的問題。而影響阻抗匹配的因素包括信號源的架構、輸出阻抗(outputimpedance)、走線的特性阻抗、負載端的特性、走線的拓樸(topology)架構等。解決的方式可以采用端接(termination)與調整走線拓樸的策略。信號完整性問題通常不是由某個單一因素導致的,而是板級設計中多種因素共同作用的結果。信號完整性問題主要表現形式包括信號反射、信號振鈴、地彈、串擾等;1,AltiumDesigner信號完整性分析(機理、模型、功能)在AltiumDesigner設計環境下。湖北了解PCB制板包括哪些

- 荊門了解PCB制板 2025-05-11

- 隨州專業PCB制板布線 2025-05-11

- 荊州了解PCB制板銷售 2025-05-11

- 武漢焊接PCB制板包括哪些 2025-05-11

- 荊門PCB制板多少錢 2025-05-11

- 荊門生產PCB制板原理 2025-05-11

- 黃岡PCB制板批發 2025-05-11

- 湖北正規PCB設計 2025-05-11

- 武漢高速PCB制板布線 2025-05-11

- 武漢如何PCB培訓批發 2025-05-10

- 上海潛伏AGV技術原理 2025-05-11

- 安徽低壓配電箱定制 2025-05-11

- 長寧區銷售晶閘管設計 2025-05-11

- 濟南純水業電力設備安裝 2025-05-11

- 四川 全國產驅動器銷售 2025-05-11

- 安徽柔性屏蔽拖鏈電纜供應商 2025-05-11

- 江西電力環境自動滅火貼牌 2025-05-11

- 靜安區生產雙色門頭屏利潤 2025-05-11

- 江蘇度假酒店門牌廠家 2025-05-11

- 南通多層車載攝像頭價格表 2025-05-11