-

借力浙江 “雙碳” 新政 晶映照明節(jié)能改造推動企業(yè)綠色轉(zhuǎn)型

-

山東“五段式”電價來襲!晶映節(jié)能燈,省電90%的秘密武器!

-

晶映照明助力重慶渝北區(qū)冉家壩小區(qū)車庫煥新顏

-

停車場改造的隱藏痛點:從 “全亮模式” 到晶映T8的智能升級

-

晶映T8:重新定義停車場節(jié)能改造新標準

-

杭州六小龍后,晶映遙遙 “領銜” 公共區(qū)域節(jié)能照明

-

晶映節(jié)能照明:推進公共區(qū)域節(jié)能照明革新之路

-

晶映:2025年停車場照明節(jié)能改造新趨勢

-

晶映助力商業(yè)照明 企業(yè)降本增效新引擎

-

晶映節(jié)能賦能重慶解放碑:地下停車場照明革新,測電先行

隨州了解PCB制板價格大全

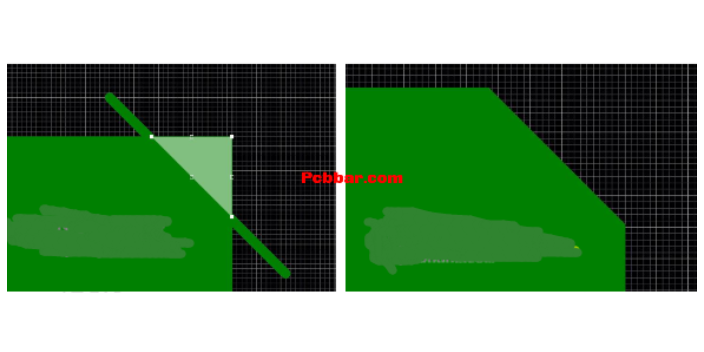

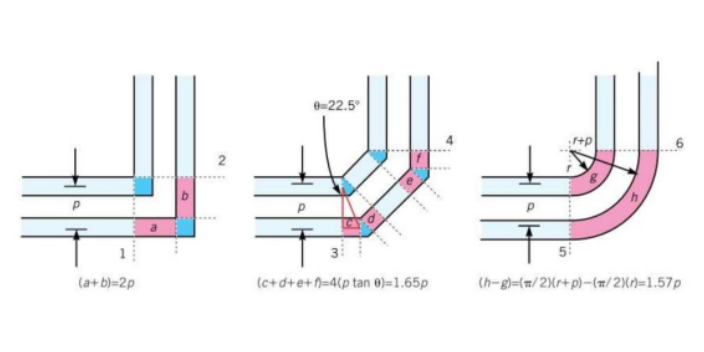

所有信號層盡可能與地平面相鄰;4、盡量避免兩信號層直接相鄰;相鄰的信號層之間容易引入串擾,從而導致電路功能失效。在兩信號層之間加入地平面可以有效地避免串擾。5、主電源盡可能與其對應地相鄰;6、兼顧層壓結構對稱。7、對于母板的層排布,現(xiàn)有母板很難控制平行長距離布線,對于板級工作頻率在50MHZ以上的(50MHZ以下的情況可參照,適當放寬),建議排布原則:元件面、焊接面為完整的地平面(屏蔽);無相鄰平行布線層;所有信號層盡可能與地平面相鄰;關鍵信號與地層相鄰,不跨分割區(qū)。注:具體PCB的層的設置時,要對以上原則進行靈活掌握,在領會以上原則的基礎上,根據(jù)實際單板的需求,如:是否需要一關鍵布線層、電源、地平面的分割情況等,確定層的排布,切忌生搬硬套,或摳住一點不放。8、多個接地的內(nèi)電層可以有效地降低接地阻抗。例如,A信號層和B信號層采用各自單獨的地平面,可以有效地降低共模干擾。常用的層疊結構:4層板下面通過4層板的例子來說明如何各種層疊結構的排列組合方式。對于常用的4層板來說,有以下幾種層疊方式(從頂層到底層)。(1)Siganl_1(Top),GND(Inner_1),POWER(Inner_2),Siganl_2(Bottom)。(2)Siganl_1(Top),POWER。PCB 制版將面臨更多的機遇與挑戰(zhàn),需要不斷探索和應用新的材料、工藝和技術,以滿足日益增長的市場需求。隨州了解PCB制板價格大全

***的PCB設計師需要***了解各種電子器件的特性和性能,根據(jù)實際需求選擇合適的元器件,并合理布局、連接電路,使得電子產(chǎn)品能夠穩(wěn)定、高效地工作。同時,PCB設計師還必須注重電磁兼容性和散熱問題,以確保電子產(chǎn)品在長時間運行過程中不會出現(xiàn)過熱或電磁干擾等問題。總之,PCB設計是電子產(chǎn)品設計中不可或缺的一環(huán),它的優(yōu)良與否直接影響著整個電子產(chǎn)品的品質(zhì)和性能。只有具備豐富的知識和經(jīng)驗,并融入創(chuàng)新思維和工藝技巧,才能設計出***的PCB電路板,為電子產(chǎn)品的發(fā)展貢獻力量。黃岡定制PCB制板功能線路設計與布局優(yōu)化:合理的線路設計和布局對于提高信號完整性和減少電磁干擾(EMI)至關重要。

10層板PCB典型10層板設計一般通用的布線順序是TOP--GND---信號層---電源層---GND---信號層---電源層---信號層---GND---BOTTOM本身這個布線順序并不一定是固定的,但是有一些標準和原則來約束:如top層和bottom的相鄰層用GND,確保單板的EMC特性;如每個信號使用GND層做參考平面;整個單板都用到的電源優(yōu)先鋪整塊銅皮;易受干擾的、高速的、沿跳變的走內(nèi)層等等。下表給出了多層板層疊結構的參考方案,供參考。PCB設計之疊層結構改善案例(From金百澤科技)問題點產(chǎn)品有8組網(wǎng)口與光口,測試時發(fā)現(xiàn)第八組光口與芯片間的信號調(diào)試不通,導致光口8調(diào)試不通,無法工作,其他7組光口通信正常。1、問題點確認根據(jù)客戶端提供的信息,確認為L6層光口8與芯片8之間的兩條差分阻抗線調(diào)試不通;2、客戶提供的疊構與設計要求改善措施影響阻抗信號因素分析:線路圖分析:客戶L56層阻抗設計較為特殊,L6層阻抗參考L5/L7層,L5層阻抗參考L4/L6層,其中L5/L6層互為參考層,中間未做地層屏蔽,光口8與芯片8之間線路較長,L6層與L5層間存在較長的平行信號線(約30%長度)容易造成相互干擾,從而影響了阻抗的度,阻抗線的設計屏蔽層不完整,也造成阻抗的不連續(xù)性,其他7組部分也有相似問題。

PCB(printed circuit board)即印制線路板,簡稱印制板,是電子工業(yè)的重要部件之一。幾乎每種電子設備,小到電子手表、計算器,大到計算機、通信電子設備、***武器系統(tǒng),只要有集成電路等電子元件,為了使各個元件之間的電氣互連,都要使用印制板。印制線路板由絕緣底板、連接導線和裝配焊接電子元件的焊盤組成,具有導電線路和絕緣底板的雙重作用。它可以代替復雜的布線,實現(xiàn)電路中各元件之間的電氣連接,不僅簡化了電子產(chǎn)品的裝配、焊接工作,減少傳統(tǒng)方式下的接線工作量,**減輕工人的勞動強度;而且縮小了整機體積,降低產(chǎn)品成本,提高電子設備的質(zhì)量和可靠性。印制線路板具有良好的產(chǎn)品一致性,它可以采用標準化設計,有利于在生產(chǎn)過程中實現(xiàn)機械化和自動化。同時,整塊經(jīng)過裝配調(diào)試的印制線路板可以作為一個**的備件,便于整機產(chǎn)品的互換與維修。目前,印制線路板已經(jīng)極其***地應用在電子產(chǎn)品的生產(chǎn)制造中。耐化學腐蝕:通過48小時鹽霧測試,工業(yè)環(huán)境穩(wěn)定運行。

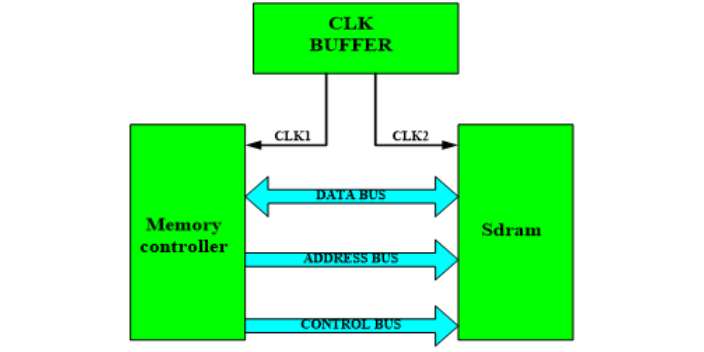

在高速數(shù)字系統(tǒng)中,由于脈沖上升/下降時間通常在10到幾百p秒,當受到諸如內(nèi)連、傳輸時延和電源噪聲等因素的影響,從而造成脈沖信號失真的現(xiàn)象;在自然界中,存在著各種各樣頻率的微波和電磁干擾源,可能由于很小的差異導致高速系統(tǒng)設計的失敗;在電子產(chǎn)品向高密和高速電路設計方向發(fā)展,解決一系列信號完整性的問題,成為當前每一個電子設計者所必須面對的問題。業(yè)界通常會采用在PCB制板前期,通過信號完整性分析工具盡可能將設計風險降,從而也促進了EDA設計工具的發(fā)展……信號完整性(SignalIntegrity,簡稱SI)問題是指高速數(shù)字電路中,脈沖形狀畸變而引發(fā)的信號失真問題,通常由傳輸線阻抗不匹配產(chǎn)生的問題。而影響阻抗匹配的因素包括信號源的架構、輸出阻抗(outputimpedance)、走線的特性阻抗、負載端的特性、走線的拓樸(topology)架構等。解決的方式可以采用端接(termination)與調(diào)整走線拓樸的策略。信號完整性問題通常不是由某個單一因素導致的,而是板級設計中多種因素共同作用的結果。信號完整性問題主要表現(xiàn)形式包括信號反射、信號振鈴、地彈、串擾等;1,AltiumDesigner信號完整性分析(機理、模型、功能)在AltiumDesigner設計環(huán)境下。HDI任意互聯(lián):1階到4階盲孔,復雜電路一鍵優(yōu)化。隨州焊接PCB制板加工

PCB制板的過程,首先需要經(jīng)過精心的設計階段。隨州了解PCB制板價格大全

4.4 成本控制在 PCB 制版過程中,成本控制是企業(yè)關注的重點之一。成本主要包括材料成本、制版成本、加工成本等多個方面。在材料選擇上,要在滿足性能要求的前提下,選擇性價比高的材料。例如,對于一些對性能要求不是特別高的消費類電子產(chǎn)品,可以選用普通的 FR - 4 覆銅板,而避免使用價格昂貴的**材料。在設計階段,通過優(yōu)化設計,減少元器件數(shù)量、簡化電路結構、合理選擇封裝形式等方式,可以降低材料成本和加工成本。例如,盡量選用通用的元器件,避免使用特殊規(guī)格或定制的元器件,以降低采購成本;采用合適的封裝形式,如表面貼裝封裝(SMT)相比傳統(tǒng)的通孔插裝封裝(THT),可以提高生產(chǎn)效率,降低焊接成本。此外,合理控制制版工藝要求,如選擇合適的線寬、線距、層數(shù)等,避免過高的工藝要求導致制版成本大幅增加。同時,與制版廠進行充分溝通,了解其報價結構和優(yōu)惠政策,通過批量生產(chǎn)、長期合作等方式爭取更優(yōu)惠的價格。隨州了解PCB制板價格大全

- 湖北打造PCB制板批發(fā) 2025-05-11

- 荊門了解PCB制板 2025-05-11

- 湖北了解PCB制板包括哪些 2025-05-11

- 隨州專業(yè)PCB制板布線 2025-05-11

- 黃岡印制PCB制板銷售電話 2025-05-11

- 荊州了解PCB制板銷售 2025-05-11

- 武漢焊接PCB制板包括哪些 2025-05-11

- 荊門PCB制板多少錢 2025-05-11

- 荊門生產(chǎn)PCB制板原理 2025-05-11

- 黃岡PCB制板批發(fā) 2025-05-11

- 建筑工地配電箱柜OEM定制 2025-05-11

- 磷酸鐵鋰鋰電池保護板保護IC 2025-05-11

- 海南BIPV防水支架規(guī)格 2025-05-11

- 上海電站太陽能全自動生產(chǎn)線有哪些 2025-05-11

- 廣東電鍍鎳層鋼卷加工中心 2025-05-11

- 金華USBPCBA設計開發(fā) 2025-05-11

- 德國weiss分度盤 2025-05-11

- 上海EOL異響檢測咨詢報價 2025-05-11

- 上海電機異響檢測應用 2025-05-11

- 國產(chǎn)尼龍推薦 2025-05-11